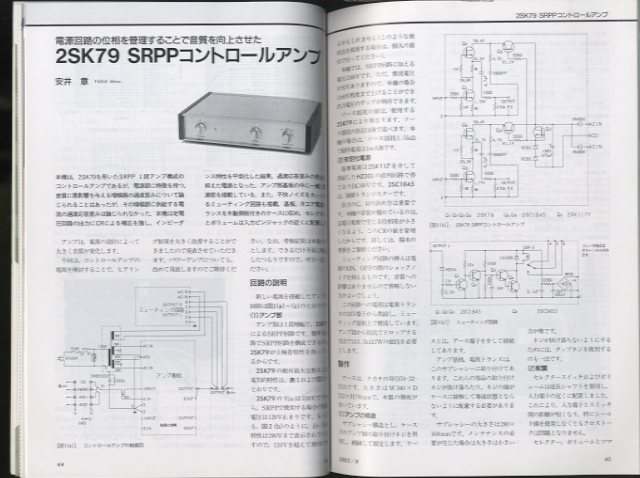

The rare Triode-like characteristics transistor made by SONY in 1970's, could be seen as a solid-state version of 12AX7 without filaments!

2002/6 MJ RADIO

R5//RV1=200R

V-FET Driver

2SK79 as input stage, 2SK60 and 2SJ49 as output stage.

Spice Models of 2SK79 VFET V-FET

For SPICE Simulation, here are some SPICE models of 2SK79 in diff formats (LTSPICE, PSPICE, etc.)

/Model A/* Created on 06/29/2020 09:20 using paint_kit.jar 3.1

* www.dmitrynizh.com/tubeparams_image.htm

* Plate Curves image file:

* Data source link:

*----------------------------------------------------------------------------------

.SUBCKT 2SK79 1 2 3 ; Plate Grid Cathode

+ PARAMS: CCG=3P CGP=15P CCP=1.9P RGI=600

+ MU=30.24 KG1=45 KP=106 KVB=337.5 VCT=0.0085 EX=1.54

* Vp_MAX=93 Ip_MAX=10 Vg_step=0.2 Vg_start=0 Vg_count=10

* Rp=2720 Vg_ac=35.48 P_max=0.5625 Vg_qui=-0.9 Vp_qui=20.25

* X_MIN=163 Y_MIN=164 X_SIZE=1080 Y_SIZE=582 FSZ_X=1936 FSZ_Y=1056 XYGrid=true

* showLoadLine=y showIp=y isDHT=n isPP=n isAsymPP=n showDissipLimit=y

* showIg1=y gridLevel2=n isInputSnapped=y

* XYProjections=n harmonicPlot=y dissipPlot=n

*----------------------------------------------------------------------------------

E1 7 0 VALUE={V(1,3)/KP*log10(1+EXP(KP*(1/MU+(VCT+V(2,3))/SQRT(KVB+V(1,3)*V(1,3)))))}

RE1 7 0 1G ; TO AVOID FLOATING NODES

G1 1 3 VALUE={(PWR(V(7),EX)+PWRS(V(7),EX))/KG1}

RCP 1 3 1G ; TO AVOID FLOATING NODES

C1 2 3 {CCG} ; CATHODE-GRID

C2 2 1 {CGP} ; GRID=PLATE

C3 1 3 {CCP} ; CATHODE-PLATE

D3 5 3 DX ; POSITIVE GRID CURRENT

R1 2 5 {RGI} ; POSITIVE GRID CURRENT

.MODEL DX D(IS=1N RS=1 CJO=10PF TT=1N)

.ENDS

.SUBCKT 2SK79 1 2 3 ; Plate Grid Cathode

+ PARAMS: CCG=3P CGP=15P CCP=1.9P RGI=600

+ MU=30.24 KG1=45 KP=106 KVB=337.5 VCT=0.0085 EX=1.54

* Vp_MAX=93 Ip_MAX=10 Vg_step=0.2 Vg_start=0 Vg_count=10

* Rp=2720 Vg_ac=35.48 P_max=0.5625 Vg_qui=-0.9 Vp_qui=20.25

* X_MIN=163 Y_MIN=164 X_SIZE=1080 Y_SIZE=582 FSZ_X=1936 FSZ_Y=1056 XYGrid=true

* showLoadLine=y showIp=y isDHT=n isPP=n isAsymPP=n showDissipLimit=y

* showIg1=y gridLevel2=n isInputSnapped=y

* XYProjections=n harmonicPlot=y dissipPlot=n

*----------------------------------------------------------------------------------

E1 7 0 VALUE={V(1,3)/KP*log10(1+EXP(KP*(1/MU+(VCT+V(2,3))/SQRT(KVB+V(1,3)*V(1,3)))))}

RE1 7 0 1G ; TO AVOID FLOATING NODES

G1 1 3 VALUE={(PWR(V(7),EX)+PWRS(V(7),EX))/KG1}

RCP 1 3 1G ; TO AVOID FLOATING NODES

C1 2 3 {CCG} ; CATHODE-GRID

C2 2 1 {CGP} ; GRID=PLATE

C3 1 3 {CCP} ; CATHODE-PLATE

D3 5 3 DX ; POSITIVE GRID CURRENT

R1 2 5 {RGI} ; POSITIVE GRID CURRENT

.MODEL DX D(IS=1N RS=1 CJO=10PF TT=1N)

.ENDS

Other Power VFET P-SPICE Models

*2SJ28

*GENERATED BY SIT MODELER @ AUDIOMAKER.TECH

*MODEL RANGE: -55V, -5A

*--------------------------------------------------

.SUBCKT 2SJ28 D G S ; Drain Gate Source

+ PARAMS: MU=7.3 X=1.51 K=0.157 N=2.24 VCT=0 RG=2MEG

*--------------------------------------------------

B1 D S I=-1*(K*PWR(URAMP((-V(G,S)+VCT)+(N*LN(-V(D,S))+(-V(D,S)/MU))),X))

*FOR LTSPICE

R1 G S {RG}

CGS G S 0P

CGD G D 0P

CDS G S 0P

.ENDS 2SJ28

*--------------------------------------------------

** 2SK82 KD-33

*M. ROTHACHER

*--------------------------------------------------

.SUBCKT 2SK82 1 2 3 ; Drain Gate Source

+ PARAMS: MU=4.9140 EX=2.352 KG1=101.25 KP=75.0 KVB=24.0 VCT=7.04 RGI=2MEG

*--------------------------------------------------

E1 7 0 VALUE={V(1,3)/KP*LN(1+EXP(KP*(1/MU+(VCT+V(2,3))/SQRT(KVB+V(1,3)*V(1,3)))))}

RE1 7 0 1G

G1 1 3 VALUE={(PWR(V(7),EX)+PWRS(V(7),EX))/KG1}

RDS 1 3 1G ; TO AVOID FLOATING NODES

D1 5 2 DX ; FOR GRID CURRENT

R1 5 3 {RGI} ; POSITIVE GRID CURRENT

.MODEL DX D(IS=1N RS=1 CJO=10PF TT=1N)

.ENDS